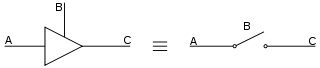

In digital electronics, a tri-state or three-state buffer is a type of digital buffer that has three stable states: a high output state, a low output state, and a high-impedance state. In the high-impedance state, the output of the buffer is disconnected from the output bus, allowing other devices to drive the bus without interference from the tri-state buffer. This can be useful in situations where multiple devices are connected to the same bus and need to take turns accessing it. Systems implementing three-state logic on their bus are known as a three-state bus or tri-state bus.

Tri-state buffers are commonly used in bus-based systems, where multiple devices are connected to the same bus and need to share it. For example, in a computer system, multiple devices such as the CPU, memory, and peripherals may be connected to the same data bus. To ensure that only one device can transmit data on the bus at a time, each device is equipped with a tri-state buffer. When a device wants to transmit data, it activates its tri-state buffer, which connects its output to the bus and allows it to transmit data. When the transmission is complete, the device deactivates its tri-state buffer, which disconnects its output from the bus and allows another device to access the bus.

Tri-state buffers can be implemented using gates, flip-flops, or other digital logic circuits. They are useful for reducing crosstalk and noise on a bus, and for allowing multiple devices to share the same bus without interference.

| INPUT | OUTPUT | |

|---|---|---|

| A | B | C |

| 0 | 0 | Z (high impedance) |

| 1 | Z (high impedance) | |

| 0 | 1 | 0 |

| 1 | 1 | |

Uses

editThe basic concept of the third state, high impedance (Hi-Z), is to effectively remove the device's influence from the rest of the circuit. If more than one device is electrically connected to another device, putting an output into the Hi-Z state is often used to prevent short circuits, or one device driving high (logical 1) against another device driving low (logical 0).

Three-state buffers can also be used to implement efficient multiplexers, especially those with large numbers of inputs.[1]

Three-state buffers are essential to the operation of a shared electronic bus.

Three-state logic can reduce the number of wires needed to drive a set of LEDs (tri-state multiplexing or Charlieplexing).

Output enable vs. chip select

editMany memory devices designed to connect to a bus (such as RAM and ROM chips) have both CS (chip select) and OE (output enable) pins, which superficially appear to do the same thing. If CS is not asserted, the outputs are high impedance.

The difference lies in the time needed to output the signal. When chip select is deasserted, the chip does not operate internally, and there will be a significant delay between providing an address and receiving the data. (An advantage of course, is that the chip consumes minimal power in this case.)

When chip select is asserted, the chip internally performs the access, and only the final output drivers are disabled by deasserting output enable. This can be done while the bus is in use for other purposes, and when output enable is finally asserted, the data will appear with minimal delay. A ROM or static RAM chip with an output enable line will typically list two access times: one from chip select asserted and address valid, and a second, shorter time beginning when output enable is asserted.

Use of pull-ups and pull-downs

editWhen outputs are tri-stated (in the Hi-Z state) their influence on the rest of the circuit is removed, and the circuit node will be "floating" if no other circuit element determines its state. Circuit designers will often use pull-up or pull-down resistors (usually within the range of 1–100 kΩ) to influence the circuit when the output is tri-stated.

The PCI local bus provides pull-up resistors, but they would require several clock cycles to pull a signal high given the bus's large distributed capacitance. To enable high-speed operation, the protocol requires that every device connecting to the bus drive the important control signals high for at least one clock cycle before going to the Hi-Z state. This way, the pull-up resistors are only responsible for maintaining the bus signals in the face of leakage current.

Intel refers to this convention as "sustained tri-state", and also uses it in the Low Pin Count bus.

Alternatives to a three-state bus

editThe open collector input/output is a popular alternative to three-state logic. For example, the I²C bus protocol (a bi-directional communication bus protocol often used between devices) specifies the use of pull-up resistors on the two communication lines. When devices are inactive, they "release" the communication lines and tri-state their outputs, thus removing their influence on the circuit. When all the devices on the bus have "released" the communication lines, the only influence on the circuit is the pull-up resistors, which pull the lines high. When a device wants to communicate, it comes out of the Hi-Z state and drives the line low. Devices communicating using this protocol either let the line float high, or drive it low – thus preventing any bus contention situation where one device drives a line high and another low.

Early microcontrollers often have some pins that can only act as an input, other pins that can only act as a push–pull output, and a few pins that can only act as an open collector input/output. A typical modern microcontroller has many three-state general-purpose input/output pins that can be programmed to act as any of those kinds of pins.

A three-state bus is typically used between chips on a single printed circuit board (PCB), or sometimes between PCBs plugged into a common backplane.

Usage of three-state logic is not recommended for on-chip connections but rather for inter-chip connections.[2]

Three-state buffers, when used to enable multiple devices to communicate on a data bus, can be functionally replaced by a multiplexer.[3] That will help select output from a range of devices and write one to the bus.

See also

editNotes and references

edit- ^ Hill, Winfield; Horowitz, Paul (1989). The Art of Electronics. Cambridge University Press. pp. 495–497. ISBN 0-521-37095-7.

- ^ 경종민, On-Chip Buses/Networks for SoC "On-Chip Buses [have] No use of tri-state signals [because] Tri-state bus is difficult for static timing analysis"

- ^ "Tri State Buffer".

External links

edit- Special-output Gates on All About Circuits

- Principle of Tristate Multiplexing