User:Imperator3733/WIP:Computing/Multi-core (computing)

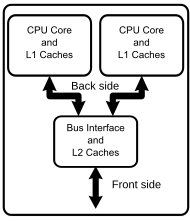

A multi-core CPU (also known as chip-level multiprocessing) is a single CPU package that contains two or more independet processing cores. These cores may be all on one die (i.e. Athlon 64 X2), each on a seperate die (i.e. Pentium D), or multiple dies each with several cores (i.e. Core 2 Quad). The CPU cores may or may not share caches, bus intefaces, or memory controllers. Multi core processors increase the total amount of execution resources available to threads.

Terminology

editThe term "multi-core" is a general term for processor packages with more than one core. "Dual-core" is used when there are just two cores in the package, "tri-core" is used with three cores, "quad-core" with four cores, "octal-core" with eight cores, etc. Therefore, a dual-core processor is a multi-core processor, although a multi-core processor is not necessarily a dual-core processor. Also, the term "multi-core" refers to a relatively small number of cores, generally no more that 10 or 16 cores. If a processor has more cores, it is normally referred to as a many-core processor.

When a processor consists of two or more seperate dies, it is refered to as a multi-chip module or MCM. If the processor has all of its cores one one die, it is called a monolithic multi-core processor.

Monolithic multi-core versus MCMs

editMonolithic multi-core processors, also known as native multi-core processors, have theoretical performance benefits over the cheaper and faster MCM processors. If a core on one die of a monolithic processor would like to communicate with another core, the signal does not need to leave the die, therby keeping the latency of the communication to a minimum. However, on an MCM, the communication may need to travel over the system bus to another die. This may affect performance when cores need to talk to each other, and it also reduces system bus bandwidth.

MCMs are cheaper to manufacture and are faster to develop than monolithic cores.

Development

editWhile manufacturing technology continues to improve, reducing the size of single gates, physical limits of semiconductor-based microelectronics have become a major design concern. Some effects of these physical limitations can cause significant heat dissipation and data synchronization problems. The demand for more capable microprocessors causes CPU designers to use various methods of increasing performance. Some instruction-level parallelism (ILP) methods like superscalar pipelining are suitable for many applications, but are inefficient for others that tend to contain difficult-to-predict code. Many applications are better suited to thread level parallelism(TLP) methods, and multiple independent CPUs is one common method used to increase a system's overall TLP. A combination of increased available space due to refined manufacturing processes and the demand for increased TLP is the logic behind the creation of multi-core CPUs.

Commercial incentives

editSeveral business motives drive the development of dual-core architectures. Since symmetric multiprocessing (SMP) designs have been long implemented using discrete CPUs, the issues regarding implementing the architecture and supporting it in software are well known. Additionally, utilizing a proven processing core design (e.g. Freescale's e700 core) without architectural changes reduces design risk significantly. Finally, the terminology "dual-core" (and other multiples) lends itself to marketing efforts.

Additionally, for general-purpose processors, much of the motivation for multi-core processors comes from greatly diminished gains in processor performance from increasing the operating frequency (frequency-scaling). The memory wall and the ILP wall are the culprits in why system performance has not gained as much from continued processor frequency increases as was once seen. The memory wall refers to the increasing gap between processor and memory speeds, which pushes cache sizes larger to mask the latency to memory which helps only to the extent that memory bandwidth is not the bottleneck in performance. The ILP wall refers to increasing difficulty to find enough parallelism in the instructions stream of a single process to keep higher performance processor cores busy. Finally, the often cited, power wall refers to the trend of consuming double the power with each doubling of operating frequency (which is possible to contain to just doubling only if the processor is made smaller). The power wall poses manufacturing, system design and deployment problems that have not been justified in the face of the diminished gains in performance due to the memory wall and ILP wall. Together, these three walls combine to motivate multicore processors.

In order to continue delivering regular performance improvements for general-purpose processors, manufacturers such as Intel and AMD have turned to multi-core designs, sacrificing lower manufacturing costs for higher performance in some applications and systems.

Multi-core architectures are being developed, but so are the alternatives. An especially strong contender for established markets is to integrate more peripheral functions into the chip.

Advantages

editThe proximity of multiple CPU cores on the same die allows the cache coherency circuitry to operate at a much higher clock rate than is possible if the signals have to travel off-chip. Combining equivalent CPUs on a single die significantly improves the performance of cache snoop (alternative: Bus snooping) operations. Put simply, this means that signals between different CPUs travel shorter distances, and therefore those signals degrade less. These higher quality signals allow more data to be sent in a given time period since individual signals can be shorter and do not need to be repeated as often.

Assuming that the die can fit into the package, physically, the multi-core CPU designs require much less Printed Circuit Board (PCB) space than multi-chip SMP designs. Also, a dual-core processor uses slightly less power than two coupled single-core processors, principally because of the increased power required to drive signals external to the chip and because the smaller silicon process geometry allows the cores to operate at lower voltages; such reduction reduces latency. Furthermore, the cores share some circuitry, like the L2 cache and the interface to the front side bus (FSB). In terms of competing technologies for the available silicon die area, multi-core design can make use of proven CPU core library designs and produce a product with lower risk of design error than devising a new wider core design. Also, adding more cache suffers from diminishing returns.

Disadvantages

editIn addition to operating system (OS) support, adjustments to existing software are required to maximize utilization of the computing resources provided by multi-core processors. Also, the ability of multi-core processors to increase application performance depends on the use of multiple threads within applications. For example, most current (as of 2006) PC games will run faster on a 3 GHz single-core processor than on a 2GHz dual-core processor (of the same core architecture),[citation needed] despite the dual-core theoretically having more processing power, because they are incapable of efficiently using more than one core at a time. The situation is improving: for example the American PC game developer Valve Corporation has stated that it will use multi core optimizations for the next version of its Source engine, shipped with Half-Life 2: Episode Two, the next installment of its Half-Life franchise[1][2], and Crytek is developing similar technologies for CryENGINE2, which powers their upcoming game, Crysis. See Dynamic Acceleration Technology for the Santa Rosa platform for an example of a technique to improve single-thread performance on dual-core processors.

Integration of a multi-core chip drives production yields down and they are more difficult to manage thermally than lower-density single-chip designs. From an architectural point of view, ultimately, single CPU designs may make better use of the silicon surface area than multiprocessing cores, so a development commitment to this architecture may carry the risk of obsolescence. Finally, raw processing power is not the only constraint on system performance. Two processing cores sharing the same system bus and memory bandwidth limits the real-world performance advantage. If a single core is close to being memory bandwidth limited, going to dual-core might only give 30% to 70% improvement. If memory bandwidth is not a problem, a 90% improvement can be expected. It would be possible for an application that used 2 CPUs to end up running faster on one dual-core if communication between the CPUs was the limiting factor, which would count as more than 100% improvement.

Hardware trend

editThe general trend in processor development has been from multi-core to many-core: from dual-, quad-, eight-core chips to ones with tens or even hundreds of cores; see manycore processing unit. In addition, multi-core chips mixed with simultaneous multithreading, memory-on-chip, and special-purpose "heterogeneous" cores promise further performance and efficiency gains, especially in processing multimedia, recognition and networking applications. There is also a trend of improving energy efficiency by focusing on performance-per-watt with advanced fine-grain or ultra fine-grain power management and dynamic voltage and frequency scaling (DVFS [disambiguation needed]).

Software impact

editSoftware benefits from multicore architectures where code can be executed in parallel. Under most common operating systems this requires code to execute in separate threads or processes. Each application running on a system runs in its own process so multiple applications will benefit from multicore architectures. Each application may also have multiple threads but, in most cases, it must be specifically written to utilize multiple threads. Operating system software also tends to run many threads as a part of its normal operation. Running virtual machines will benefit from adoption of multiple core architectures since each virtual machine runs independently of others and can be executed in parallel.

Most application software is not written to use multiple concurrent threads intensively because of the challenge of doing so. A frequent pattern in multithreaded application design is where a single thread does the intensive work while other threads do much less. For example, a virus scan application may create a new thread for the scan process, while the GUI thread waits for commands from the user (e.g. cancel the scan). In such cases, multicore architecture is of little benefit for the application itself due to the single thread doing all heavy lifting and the inability to balance the work evenly across multiple cores. Programming truly multithreaded code often requires complex co-ordination of threads and can easily introduce subtle and difficult-to-find bugs due to the interleaving of processing on data shared between threads (thread-safety). Consequently, such code is much more difficult to debug than single-threaded code when it breaks. There has been a perceived lack of motivation for writing consumer-level threaded applications because of the relative rarity of consumer-level multiprocessor hardware. Although threaded applications incur little additional performance penalty on single-processor machines, the extra overhead of development has been difficult to justify due to the preponderance of single-processor machines.

As of September 2006, with the typical mix of mass-market applications the main benefit to an ordinary user from a multi-core CPU will be improved multitasking performance, which may apply more often than expected. Ordinary users are already running many threads; operating systems utilize multiple threads, as well as antivirus programs and other 'background processes' including audio and video controls. The largest boost in performance will likely be noticed in improved response time while running CPU-intensive processes, like antivirus scans, defragmenting, ripping/burning media (requiring file conversion), or searching for folders. For example, if the automatic virus scan initiates while a movie is being watched, the movie is far less likely to lag, as the antivirus program will be assigned to a different processor than the processor running the movie playback.

Given the increasing emphasis on multicore chip design, stemming from the grave thermal and power consumption problems posed by any further significant increase in processor clock speeds, the extent to which software can be multithreaded to take advantage of these new chips is likely to be the single greatest constraint on computer performance in the future. If developers are unable to design software to fully exploit the resources provided by multiple cores, then they will ultimately reach an insurmountable performance ceiling.

The telecommuncation markets had been one of the first that needed a new design of parallel datapath packet processing because there were a very quick adoption of these multiple core processors for the datapath and the control plane. These MPUs are going to replace the traditional Network Processors that were based on proprietary micro- or pico- code. 6WIND was the first company to provide embedded software for these applications.

Parallel programming techniques can benefit from multiple cores directly. Some existing parallel programming models such as OpenMP and MPI can be used on multi-core platforms. Intel introduced a new abstraction for C++ parallelism called TBB. Other research efforts have been seen also, like the Codeplay Sieve System, Cray's Chapel, Sun's Fortress, and IBM's X10.

Concurrency acquires a central role in true parallel application. The basic steps in designing parallel applications are:

- Partitioning

- The partitioning stage of a design is intended to expose opportunities for parallel execution. Hence, the focus is on defining a large number of small tasks in order to yield what is termed a fine-grained decomposition of a problem.

- Communication

- The tasks generated by a partition are intended to execute concurrently but cannot, in general, execute independently. The computation to be performed in one task will typically require data associated with another task. Data must then be transferred between tasks so as to allow computation to proceed. This information flow is specified in the communication phase of a design.

- Agglomeration

- In the third stage, we move from the abstract toward the concrete. We revisit decisions made in the partitioning and communication phases with a view to obtaining an algorithm that will execute efficiently on some class of parallel computer. In particular, we consider whether it is useful to combine, or agglomerate, tasks identified by the partitioning phase, so as to provide a smaller number of tasks, each of greater size. We also determine whether it is worthwhile to replicate data and/or computation.

- Mapping

- In the fourth and final stage of the parallel algorithm design process, we specify where each task is to execute. This mapping problem does not arise on uniprocessors or on shared-memory computers that provide automatic task scheduling.

On the other hand, on the server side, multicore processors are ideal because they allow many users to connect to a site simultaneously and have independent threads of execution. This allows for Web servers and application servers that have much better throughput.

Licensing

editTypically, proprietary enterprise server software is licensed "per processor". In the past a CPU was a processor and most computers had only one CPU, so there was no ambiguity.

Now there is the possibility of counting cores as processors and charging a customer for multiple licenses for a multi-core CPU. However, the trend seems to be counting dual-core chips as a single processor as Microsoft, Intel, and AMD support this view. Microsoft have said they would treat a socket as a single processor. [citation needed]

Oracle counts an AMD or Intel dual-core CPU as a single processor but has other numbers for other types, especially for processors with more than 2 cores. IBM, HP and Microsoft count a multi-chip module as multiple processors. If multi-chip modules count as one processor, CPU makers have an incentive to make large expensive multi-chip modules so their customers save on software licensing. So it seems that the industry is slowly heading towards counting each die (see Integrated circuit) as a processor, no matter how many cores each die has. Intel has released Paxville which is really a multi-chip module but Intel is calling it a dual-core - because it uses only one socket. It is not clear yet how licensing will work for Paxville. This is an unresolved and thorny issue for software companies and customers of proprietary software.

Embedded Applications

editA distinct area of processor technology from "mainstream" PCs is that of embedded computing. The same technological drivers towards multicore apply here too. Indeed, in many cases the application is a "natural" fit for multicore technologies, if the task can easily be partitioned between the different processors.

In network processing, it is now mainstream for devices to be multi-core, with companies such as Cavium, Wintegra and Broadcom all manufacturing products with eight processors. In digital signal processing the same trend applies: Texas Instruments has the three-core TMX320C6488, Freescale the four-core MSC8144 (and both have stated they are working on eight-core successors). Newer entries include the Storm-1 family from Stream Processors, Inc with 40 and 80 general purpose ALUs per chip, all programmable in C as a SIMD engine and Picochip with three-hundred processors on a single die, focused on communication applications.

Hardware

editThe following is a list of multi-core microprocessors listed by manufacturer.

Consumer multi-core microprocessors

edit- Pentium D -- Dual-core version of the Pentium 4

- Core Duo -- Dual-core version of the Pentium M

- Core 2 Duo -- Dual-core mainstream microprocessor based on the Core microarchitecture

- Core 2 Quad -- Quad-core mainstream microprocessor based on the Core microarchitecture

- Core 2 Extreme -- Dual- and Quad-core enthusiast microprocessors based on the Core microarchitecture

Server multi-core microprocessors

edit- Xeon -- Recent models are dual- or quad-core microprocessors

- Itanium 2 -- Recent models are dual-core microprocessors

Consumer multi-core microprocessors

edit- Athlon 64 X2 -- Dual-core version of the Athlon 64

- Athlon 64 FX -- Some models are dual-core processors

- Turion 64 X2 -- Dual-core version of the Turion 64 mobile processor

- Phenom FX -- Quad-core K10 based processor

- Phenom X4 -- Quad-core K10 based processor

- Phenom X2 -- Dual-core K10 based processor

Server multi-core microprocessors

editConsumer multi-core microprocessors

edit- PowerPC 970MP -- Dual-core version of the PowerPC 970 (aka G5)

- STI Cell -- Nine-core microprocessor used in Sony's PlayStation 3 game console.

- Xenon -- Tri-core microprocessor used in Microsoft's Xbox 360 game console

Server multi-core microprocessors

editCommercial examples

edit| This section may require cleanup to meet Wikipedia's quality standards. No cleanup reason has been specified. Please help improve this section if you can; the talk page may contain suggestions. |

Hardware

edit- Chip Comparison Chart (Additions welcome)

- AMD released its dual-core Opteron server/workstation processors on 22 April 2005, and its dual-core desktop processors, the Athlon 64 X2 family, were released on 31 May 2005. AMD have also recently released the Athlon 64 FX line as FX-60, FX-62 and FX-64 for high performance desktops, and Turion 64 X2 for laptops. AMD announced [3] its quad-core and triple-core [4] processors would be produced in end of 2007 to beginning of 2008. With multi-cores architecture evolve, future processors will incorporate a DirectX and OpenGL capable graphics core (AMD Fusion) with at least two cores, at the same time server processors will see an 8-core or more configurations due in 2009 with the Bulldozer processor core.

- ARM MPCore is a fully synthesizable multicore container for ARM9 and ARM11 processor cores, intended for high-performance embedded and entertainment applications.

- Broadcom SiByte (SB1250, SB1255, SB1455)

- Cradle Technologies multi-core DSP processor (CT3400, CT3600)

- Cavium Networks' Octeon MPU has 16 MIPS cores.

- The Cell processor manufactured by IBM, Sony, and Toshiba used in the Sony PlayStation 3 has a general purpose PowerPC based core (PPE) and 8 specialized cores optimized for vector operations.

- International Business Machines (IBM)'s POWER4, first Dual-Core module processor released in 2000 and POWER5 dual-core chip is now in production, and the company has a PowerPC 970MP dual-core processor in production that was used in the Apple Power Mac G5.

- Intel launched its quad core processor on 13th Dec 2006 and is currently shipping Core 2 Quad and Xeon microprocessors with quad-core technology codenamed "Kentsfield". Also Core Duo, Core 2 Duo, and Xeon (x1xx series) microprocessors with dual-core technology. These chips, were based on the Pentium M (Core Duo) and Core (Core 2 Duo and Xeon), the Pentium D chips are based on the Pentium 4.

- Itanium 2 multi-core processor: Montecito (processor)

- Intel has developed an 80-core processor prototype that has each core running at 3.16GHz, which it says will be released within the next five years.[5]

- Microsoft's Xbox 360 game console uses a triple core SMT-capable PowerPC microprocessor, Xenon, made by IBM.

- Motorola/Freescale has dual-core ICs based on the PowerPC e200, e500 and G4/e600 cores, and the e700 core under development.

- Picochip has a family of multi-core DSP devices, with over 300 16-bit processor MIMD cores on one die. These products are optimized for wireless.

- The Parallax Propeller is a cheap and simple multiprocessing microcontroller with eight 32 bit cores controlled by an internal bus controller. It uses the proprietary Spin computer language.

- PA-RISC (PA-8800)

- Raza Microelectronics' XLR MPU has eight MIPS cores.

- Stream Processors' Storm-1 family with 2 MIPS CPUs and one large DSP for video applications.

- Sun Microsystems

- UltraSPARC IV,

- UltraSPARC IV+,

- UltraSPARC T1 eight cores, 32 threads

- UltraSPARC T2 eight cores, 64 concurrent threads

- Tilera release its 64-core processor on August 20, 2007.

- Many of the chip designs of Chuck Moore were multi-core stack machines. IntellaSys markets his latest 24 core design, the seaForth-24.

Software

editNotes

edit- ^ Digital signal processors, DSPs, have utilized multi-core architectures for much longer than high-end general purpose processors. A typical example of a DSP-specific implementation would be a combination of a RISC CPU and a DSP MPU. This allows for the design of products that require a general purpose processor for user interfaces and a DSP for real-time data processing; this type of design is common in mobile phones.

In other applications, a growing number of companies have developed multi-core DSPs with very large numbers of processors.

- ^ Two types of operating systems are able to utilize a dual-CPU multiprocessor: partitioned multiprocessing and symmetric multiprocessing (SMP). In a partitioned architecture, each CPU boots into separate segments of physical memory and operate independently; in an SMP OS, processors work in a shared space, executing threads within the OS independently.

See also

edit- Multithreading (computer hardware)

- Many-core processing unit

- Multiprocessing

- Hyper-threading

- Symmetric multiprocessing (SMP)

- Simultaneous multithreading (SMT)

- multitasking

- Parallel computing

- Other MIMD-on-a-chip processors ( Multi-core processors) include

- TMS320C80 MVP (multimedia video processor)

- Kilocore

- Emotion Engine

- graphics processing unit

- the Parallax Propeller

- sometimes multiple CPUs are placed on a single FPGA

- Agiea Phys X Chip

References

edit- ^ [1]

- ^ [2]

- ^ Quad-cores from AMD

- ^ AMD announcement, retrieved September 17, 2007

- ^ 80-core prototype from Intel

External links

edit- Windows XP Multi Core config - Does your OEM do it for you? configuring XP (32-bit) to fully utilize multi-core CPUs.

- A discussion with Andre LaMothe on multi-core programming - electricalfun.com

- A Berkeley View on the Parallel Computing Landscape Argues for the desperate need to innovate around "manycore".

- Multi-core Computing course by Rice University.

- PARLANSE Parallel programming for x86 family multicore processors

- BMDFM: Binary Modular Dataflow Machine - Multi-core Runtime Environment (BMDFM)

- Intel Tera-scale Computing Research Program

- Discovering Multi-Core: Extending the Benefits of Moore’s Law

- AMD HyperTransport Technology

- Intel First to Ship Dual Core x86 chip – By Michael Singer, internetnews.com, 12 April 2005

- Findings of a test carried out by Anandtech showed that dual-core chips produced by AMD and Intel had individual performance merits under different situations of application

- Hyper-parallel data processing Java framework

- The Multicore Association, an industry group focusing on multitasking APIs, communication APIs, and debugging in multicore environments.

- CMP news articles and academic papers

- Sun Studio multithreading tools for Solaris OS and Linux

- "Public Asked to Help Name New Technology: 64 parallel processors on one chip"

- "Four Core and Seven Years Ago"